Exemple de conception

On doit concevoir un circuit séquentiel qui détecte la séquence binaire 101 lorsqu’elle apparaît dans sa séquence d’entrée. Une fois la séquence identifiée, le système produira une sortie 1 et demeurera dans le même état en continuant de produire une sortie 1, jusqu’à une remise à zéro.

Bascules D

Diagramme d’état

Selon le diagramme d’état de la figure ci-dessous, le système démarre dans l’état a et demeure dans cet état tant que l’entrée \(A=0\). Lorsque \(A=1\), on passe à l’état b, début de la reconnaissance du patron 101. Ensuite, si \(A=1\), on reste dans l’état b parce que ce pourrait être le début d’une autre séquence 101. De l’état b, si \(A=0\), on passe à l’état c, car on a observé 10 en séquence. De l’état c, si on a \(A=0\), la séquence observée est maintenant de 100 et on doit tout recommencer en retournant à l’état a. De l’état c, si on a \(A=1\), alors on a reconnu la séquence 101. On met la sortie \(S=1\) et on reste dans cet état pour toutes les autres transitions, quelle que soit l’entrée. Il s’agit ici d’une machine de Moore, puisque la sortie est \(S=1\) produite lorsqu’on est dans l’état d ; on a \(S=0\) dans les autres états.

Réduction d’états

Il n’y a pas de réduction d’états possible ici.

Assigner des codes binaires aux états

Pour quatre états, il nous faudra deux bascules. Le tableau 6 présente l’assignation d’états choisie.

| État | Code |

|---|---|

| a | 00 |

| b | 01 |

| c | 10 |

| d | 11 |

Remplir le tableau de transition

Le tableau 7 donne les transitions d’états.

| $$ Z_1^n$$ | $$ Z_0^n$$ | $$ A$$ | $$ Z_1^{n+1}$$ | $$ Z_0^{n+1}$$ | $$ S$$ | |

|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | |

| 0 | 0 | 1 | 0 | 1 | 0 | |

| 0 | 1 | 0 | 1 | 0 | 0 | |

| 0 | 1 | 1 | 0 | 1 | 0 | |

| 1 | 0 | 0 | 0 | 0 | 0 | |

| 1 | 0 | 1 | 1 | 1 | 0 | |

| 1 | 1 | 0 | 1 | 1 | 1 | |

| 1 | 1 | 1 | 1 | 1 | 1 |

Sélectionner un type de bascules à utiliser

On choisit des bascules D.

Déterminer les expressions simplifiées

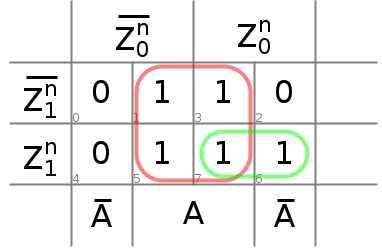

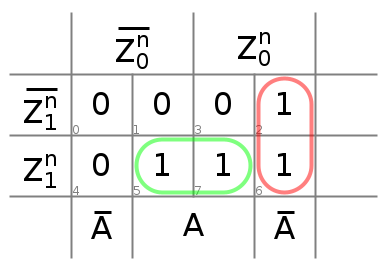

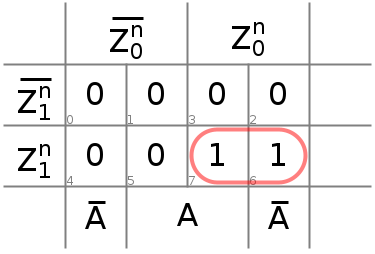

Les diagrammes de Karnaugh correspondants sont donnés ci-dessous pour \(Z_0^{n+1}\), \(Z_1^{n+1}\) et \(S\).

Notons que la convention d’étiquetage des diagrammes est différente de ce que nous avons vu précédemment. Au lieu d’étiqueter les lignes et les colonnes avec bits de minterms, on indique ici à l’extérieur du diagramme proprement dit les variables (telles quelles ou complémentées) et les régions du diagramme où on les retrouve.

Diag-K pour \(Z_0^{n+1}\)

Diag-K pour \(Z_0^{n+1}\)

Diag-K pour \(Z_1^{n+1}\)

Diag-K pour \(Z_1^{n+1}\)

Diag-K pour \(S\)

Diag-K pour \(S\)

Décodeur de prochain état

Les expressions pour le décodeur de prochain état sont:

\[Z_1^{n+1} = (A^\prime \cdot Z_0^{n}) + (A \cdot Z_1^{n})\] \[Z_0^{n+1} = A + (Z_0^{n} \cdot Z_1^{n})\]Décodeur de sortie

L’expression pour le décodeur de sortie est:

\[S = Z_0^{n} \cdot Z_1^{n}\]Tracer le schéma logique du circuit

Le circuit obtenu est représenté sur la figure suivante.

On montre ensuite deux traces d’exécution. Sur la première trace d’exécution, pendant les premiers coups d’horloge, l’entrée \(A=0\) et le système demeure dans l’état 0. Puis, lorsque \(A=1\), on passe à l’état 1. Comme \(A\) reste à 1, on demeure dans l’état 1 un certain temps. Puis, lorsque \(A=0\), on passe à l’état 2. Avec \(A=1\) de nouveau, on passe à l’état 3 en activant la sortie \(S=1\). On ne quittera plus cet état ensuite.

La deuxième trace d’exécution montre un cas où le système retourne à l’état 0 après avoir reçu une séquence 100.